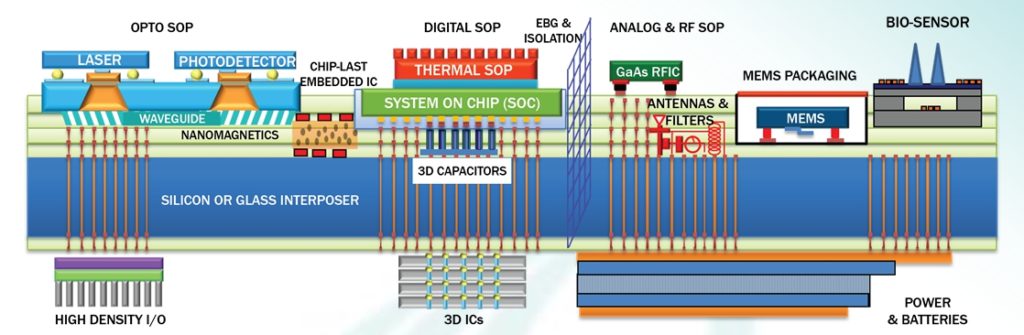

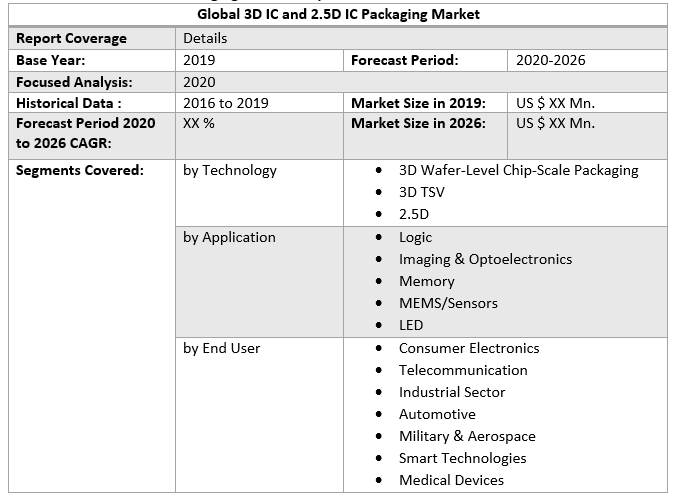

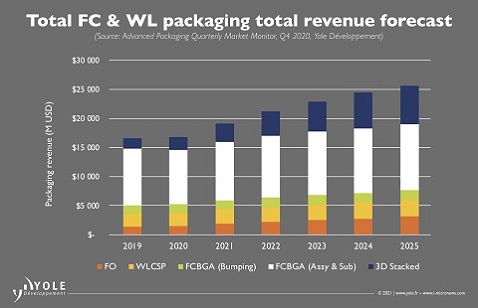

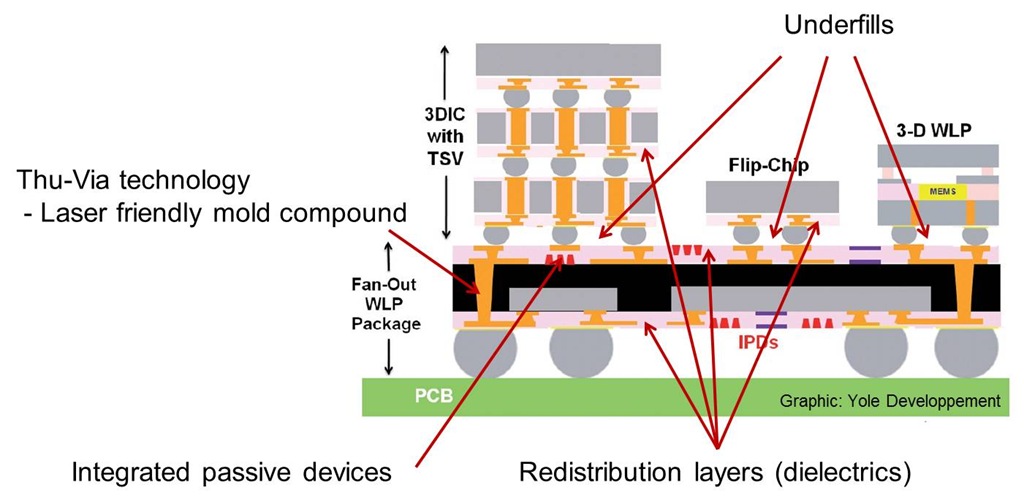

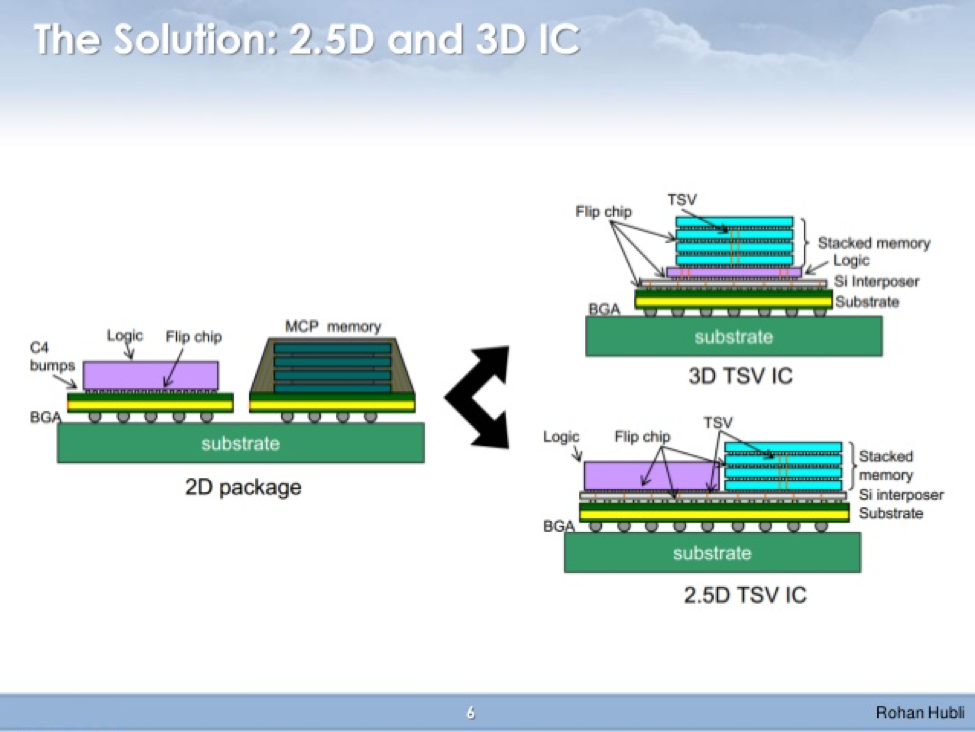

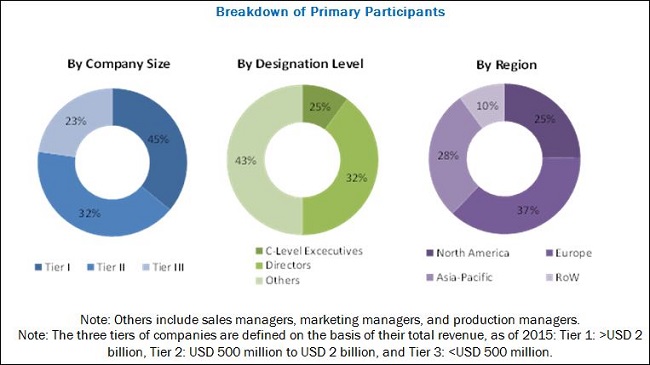

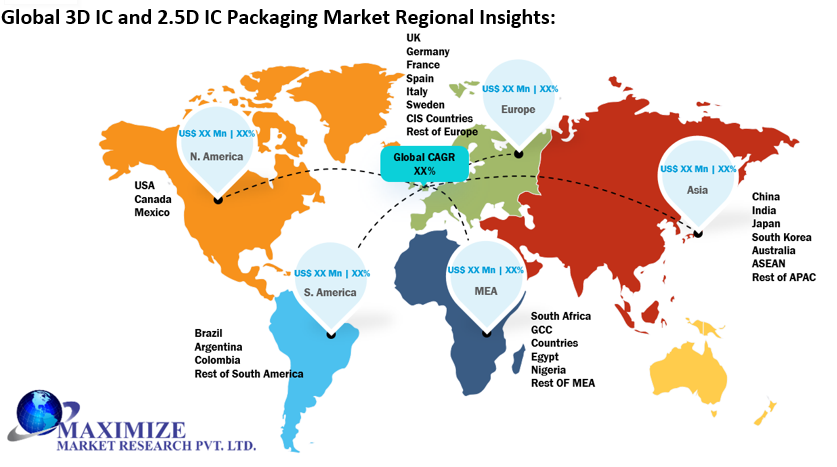

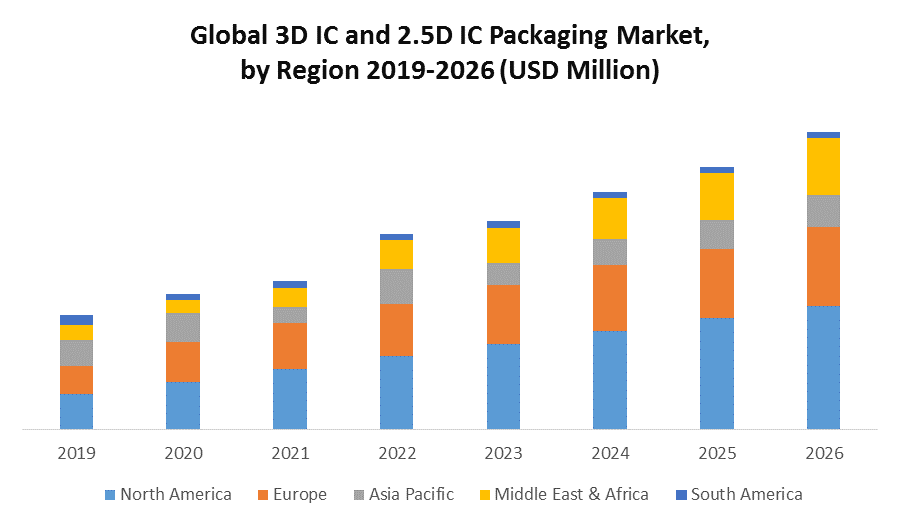

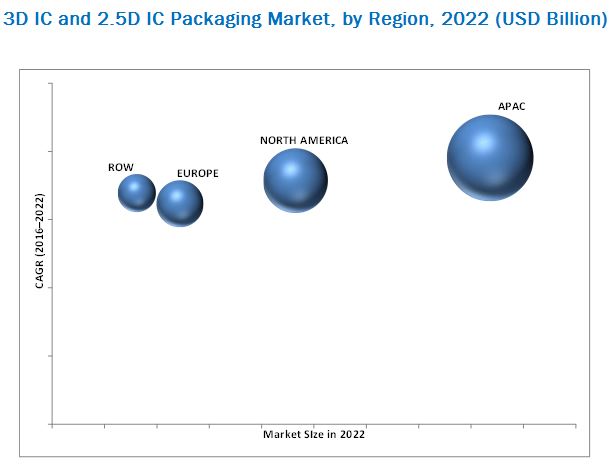

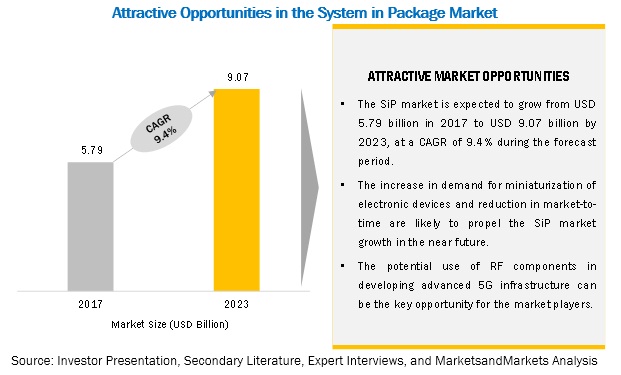

The overall IC packaging market is projected to reach $68 billion in 19, up 35% over 18, according to Yole Développement Of those figures, advanced packaging is projected to grow at 43% in 19, compared to 28% for traditional/commodity packaging, according to Yole More 25D/3D and chiplets IC packaging is important for several reasons3D TSV in market is estimated to grow at the highest CAGR during the forecast period The major factors driving the 3D IC and 25D IC market for 3D TSV include highest interconnect density and greater space efficiencies in 3D TSV compared to all other types of advanced packaging, such as 3D WLCSP and 25 D25/3D wafer level packaging is one of the important key technologies in advanced microelectronic packaging and system integration worldwide This concept has specific advantages in terms of heterogeneous integration of multiple devices such as sensors, processors, memory ICs and transceivers with excellent electrical performance and small form factor

About 2 5d Technology Nhanced Semiconductors Inc

2.5 3d packaging

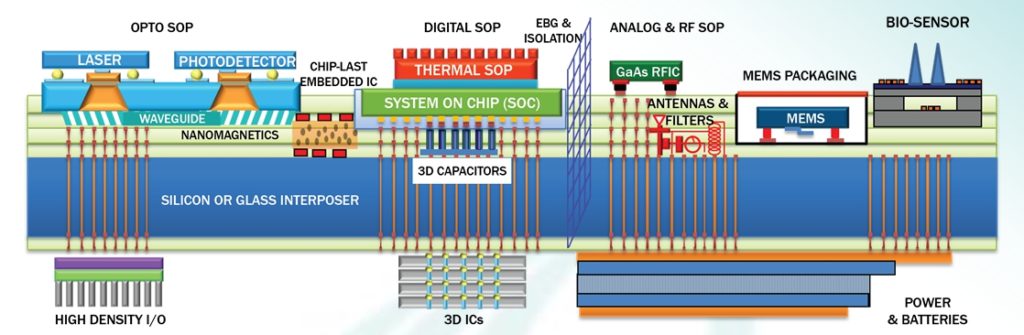

2.5 3d packaging-This study explored Through Glass Via (TGV) Formation Technology by using Focused Electrical Discharging Method for alkalifee glass which has well matched CTE with Si 25D/3D Packaging has presently attracted lots of attention, an interposer is recognized as one of key materials, and its development of new fine pitch, high dense, and low cost interposer areThe 3D IC and 25D IC Packaging Market 18 research by Market Study Report It offers a feasibility analysis for investment and returns supported with data on development trend analysis across important regions of the world

Eetimes 3d Ic Design

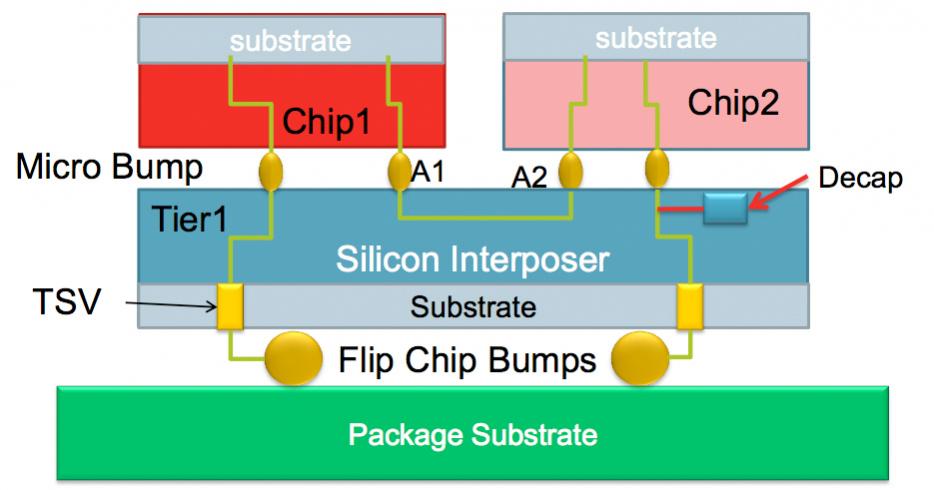

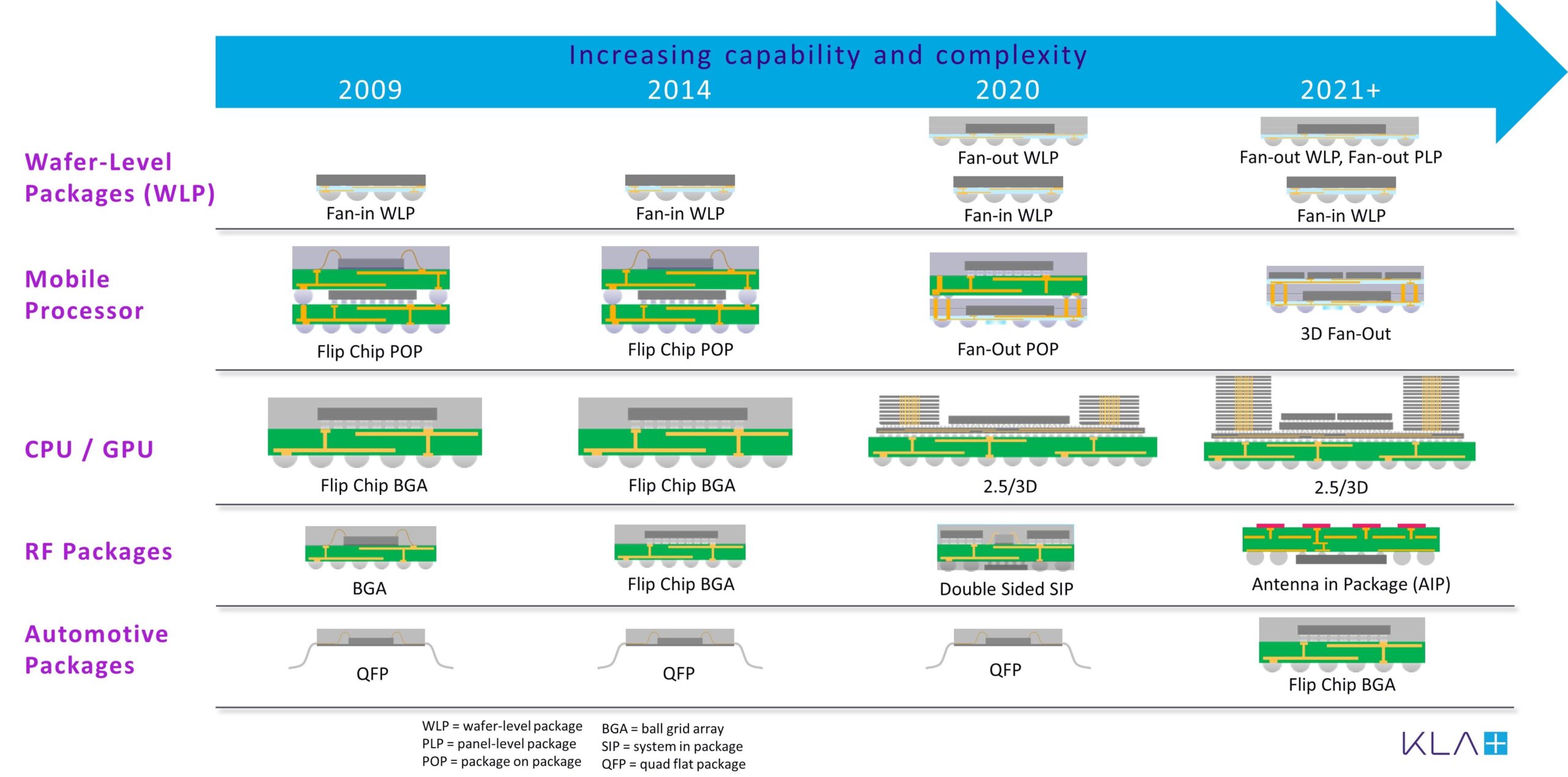

Figure 1 25/3D stack packaging technology roadmap with maturity status (C4 is controlled collapsible chip connector) A literature survey indicates that most prominent failures for COTS 3D packages and assemblies are due to warpages (individual or system) for plastic packages For the stack ceramic package and TMV™, failures• 25/3D packaging process and materials are more sophisticated than in the traditional flip chip packaging technology o The industry mainstream SoA 25/3D package assembly process, materials, and business model are not currently compatible with low volume production for mil/space components3D packaging Using a System Technology CoOptimization (STCO) approach for 25/3D Heterogeneous Semiconductor Integration

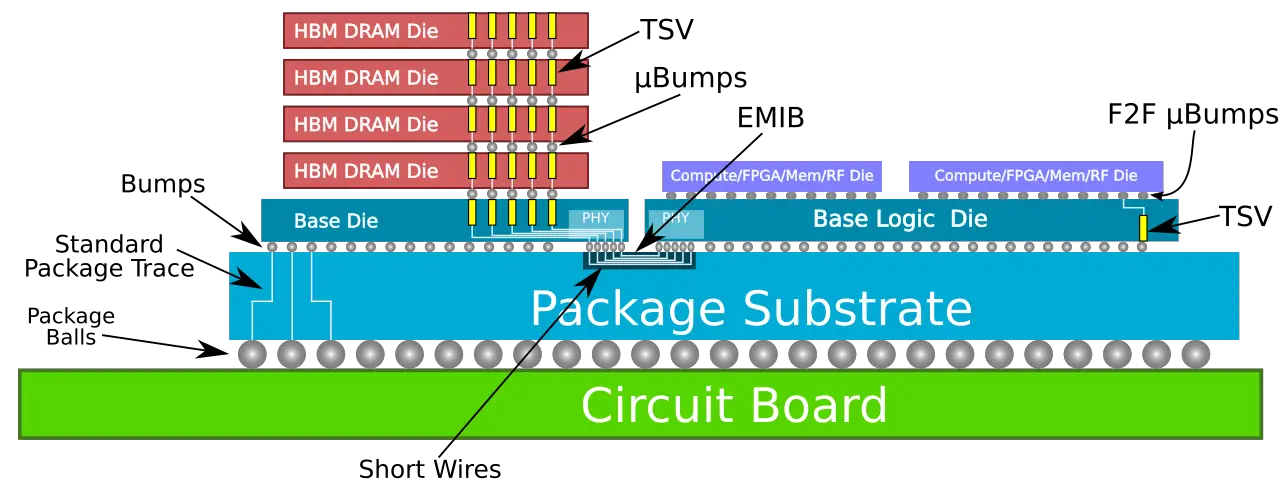

Stirring up interest in heterogeneous integration, 3D InCites follows developments in 3D IC technologies and 3D packaging, particularly focused on 3D TSVsASE is one of the pioneers in 25D/3D packaging technology and has successfully introduced the mass production of the world's first 25D IC package equipped with High Bandwidth Memory (HBM) 25D refers to die stacking package using interposers to achieve the best performance of internet connectivity An Si interposer with TSV (Through SiliconFollow along while we create this cosmetics packaging presentation from start to finish all in just an hour!

Samsung Foundry Certifies Cadence System Analysis and Advanced Packaging Design Tool Flow for 25/3D Chip Designs Proven flow featuring the Celsius Thermal Solver and Clarity 3D Solver accelerates 25/3D designs for hyperscale, communications and automotive applications SAN JOSE, Calif, December 16,Download Citation Packaging Materials for 25/3D Technology The age of advanced mobile devices is on the direct horizon, are we ready for it?25D (twoandahalf dimensional, alternatively pseudo3D or threequarter) perspective refers to one of two things Gameplay or movement in a video game or virtual reality environment that is restricted to a twodimensional (2D) plane with little to no access to a third dimension in a space that otherwise appears to be threedimensional;

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Globalfoundries Webinar Advanced 2 5d And 3d Packaging Youtube

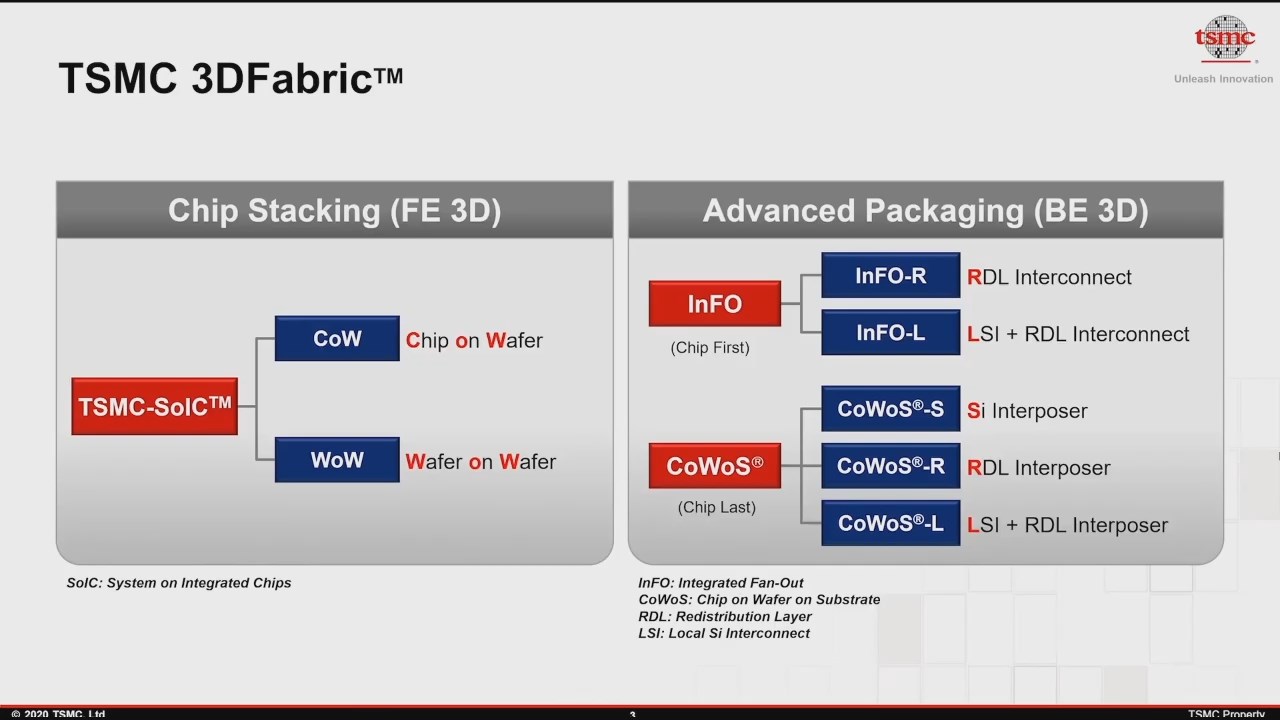

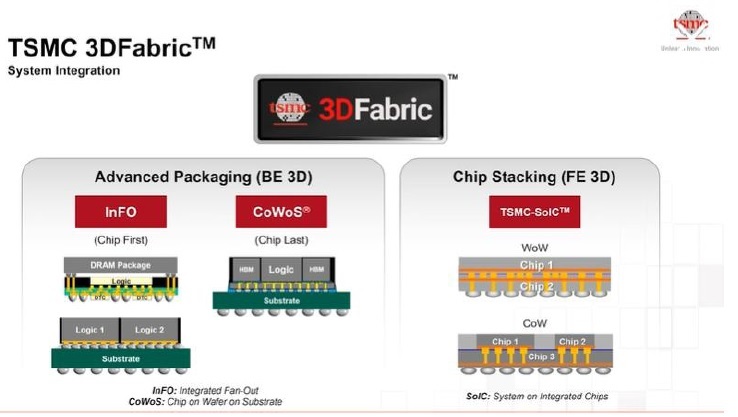

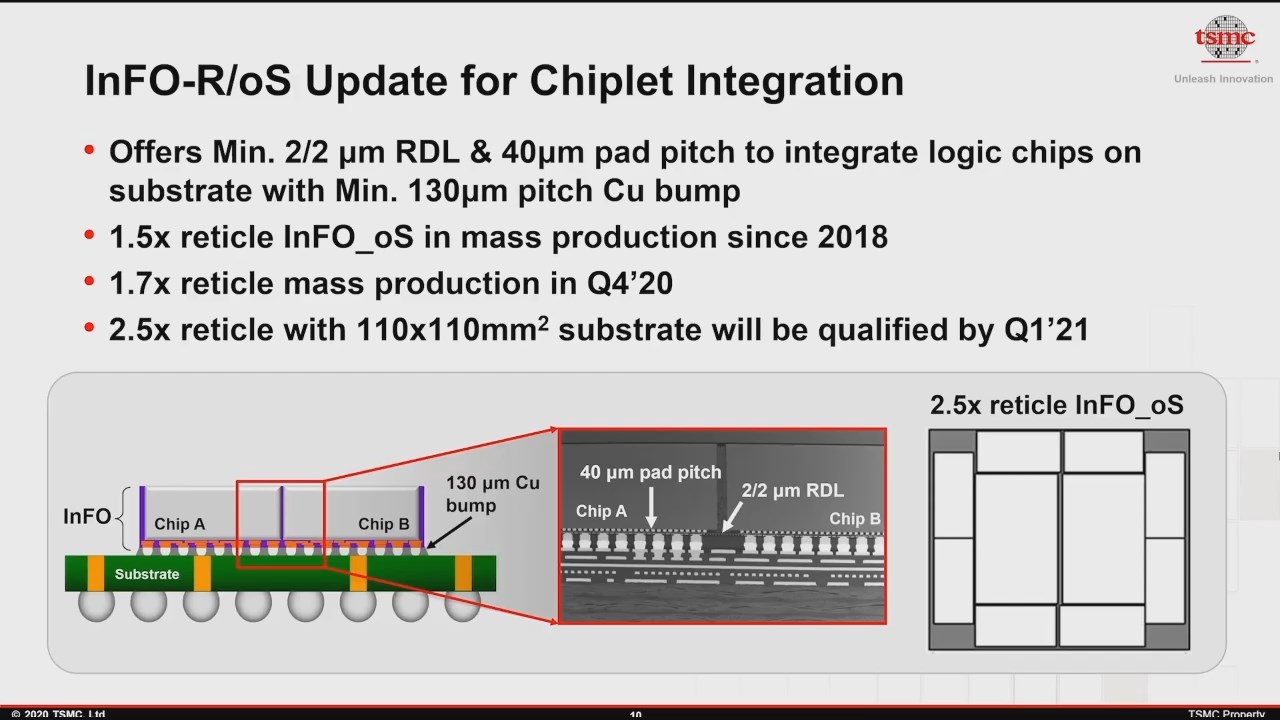

I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICs" in the title, but when I plunge in I realize that we're really only talking about 25D ICsIn order to unify all the different names it gives to its variants of its 25D and 3D packaging, TSMC has introduced its new overriding brand 3DFabric 3DFabric makes sense as a brand to tie theMarket valuation of key highend packaging technologies 3D SoC, 3D stacked memory, 25D interposers, UHD FO, embedded Si bridge;

Ewh Ieee Org

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

Highend performance packaging market segmentation;This essential volume equips readers with an indepth understanding of all aspects of 3D packaging, including packaging architecture, processing, thermal mechanical and moisture related reliability concerns, common failures, developing areas, and future challenges, providing insights into key areas for future research and development Provides3D Packaging Cost Model Which applications are right for this technology?

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

1

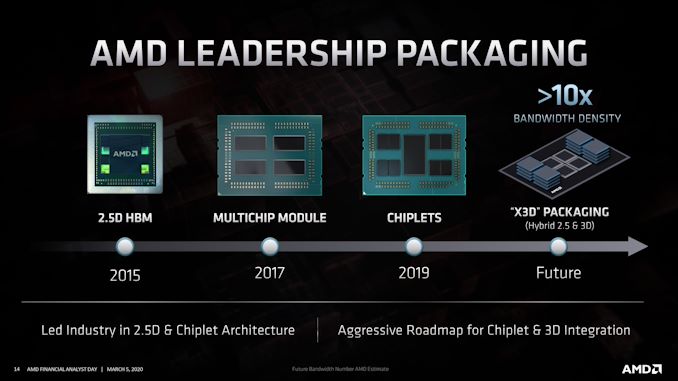

AMD Discusses 'X3D' Die Stacking and Packaging for Future Products Hybrid 25D and 3D One of AMD's key messages at its Financial Analyst Day isGlobal 3D semiconductor packaging market size is estimated to reach $ billion by 22, growing at a CAGR of 157 % from 16 to 22 3D semiconductor packaging refers to an advanced packaging technology of semiconductor chips in which two or more layers of active electronic components are stacked together and interconnected vertically as well as horizontallySignal integrity prototyping in system technology cooptimization (STCO) High Density Advanced Packaging (HDAP) using chiplets &

Circuitinsight Com

High End Packaging Intel And Tsmc Are Competing What Will Be The Strategy Of Samsung And The Others I Micronews

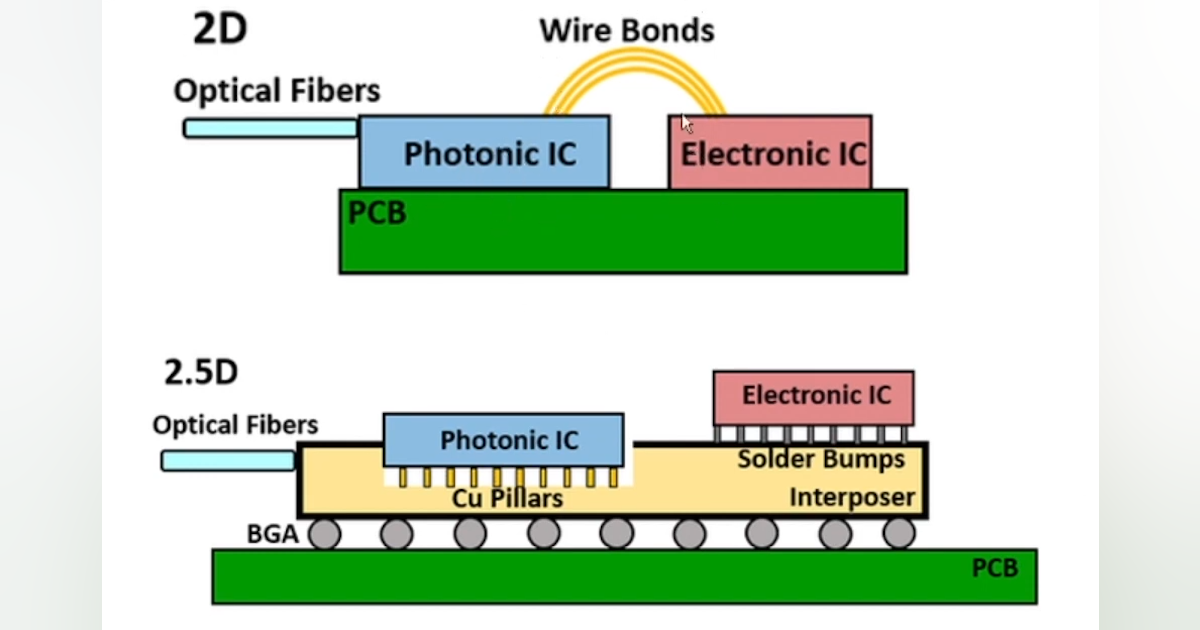

David Schor 25D packaging, 3D packaging, CoEMIB, EMIB, Foveros, Intel A look at ODI, a new family of packaging interconnect technologies that bridges the gap between Intel's EMIB (25D) and Foveros (3D) by providing the flexibility of an EMIB in 3D with additional benefits of thermal &Samsung Foundry Certifies Cadence System Analysis and Advanced Packaging Design Tool Flow for 25/3D Chip Designs Proven flow featuring the Celsius Thermal Solver and Clarity 3D Solver accelerates 25/3D designs for hyperscale, communications and25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communication While communication between chips

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

2 5d Ics Or Interposer Technology Youtube

3D Packaging Indium Corporation is a world leader in the design, formulation, manufacture and supply of semiconductorgrade fluxes and associated materials, enabling 25 and 3D assembly processes, as well as more standard flipchip assembly Stencil technology has evolved throughout the years, and SysteminPackage solder pastes require25/3D IC Packaging Technologies Part 1 Overview IEEE/CPMT, Herb Reiter eda2asic Consulting IncHerb Reiter, eda2asic Consulting, Inc herb@eda2asiccom 1 eda2asic AGENDA Part 1 Introduction Why Complement "2D Silicon Designs" withThe Evolution of MultiChip Packaging from MCMs to 25/3D to Photonics David McCann

Advanced Packaging Market To Grow 8 To 26 10 07 Packaging Strategies

1

Through Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and architectures that demand very high performance and functionality at the lowest energy/performance metric To enable the use of TSVs in 25D/3D TSV architectures, we have developed several backend technology platforms toWhen someone says, "25D packaging" my first thought is TSMC and my second thought is Herb Reiter Herb has more than 40 years of semiconductor experience and he has been a tireless promoter of 25D packaging for many years Herb writes for and works with industry organizations on 25D work groups and events at conferences Read More25D/3D packaging I've spent most of my career in the ASIC business In 03, Gartner predicted the ASIC market would grow to $169B During that time, there were a number of startups building ASICs, but the applications were a bit specialized and aimed at new markets

2 5d Packaging Wikichip Fuse

2 5d Fo Wlp Issues Come Into Focus

The major factors driving the 3D IC and 25D IC packaging market for 3D TSV include highest interconnect density and greater space efficiencies in 3D TSV compared to all other types of advanced packaging such as 3D WLCSP and 25 D The demand for 3D IC and 25D IC packages in logic is growing because of the high product availability AnChip Packaging Part 4 25D and 3D Packaging Dr Navid Asadi's group examines 25D and 3D packaging for expanding capabilities and capacities of chip solutions Peter XiMarket valuation based on topdown and bottomup models in package units, revenue and wafer production volumes;

Figure 1 From 2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

Packaging Wars Begin

Xpedition IC Packaging VX210 delivers capabilities targeted at the prototyping, planning, and design of nextgeneration 25/3D heterogeneous packages Learn about all of the new features and enhancements of the VX210 releaseCrucial BX500 480GB 3D NAND SATA 25Inch Internal SSD, up to 540MB/s CT480BX500SSD1Z Western Digital 1TB WD Blue 3D NAND Internal PC SSD SATA III 6 Gb/s, 25/7mm, Up to 560 MB/s WDS100T2B0A Add to Cart• 3D TSV and 25 packaging platforms are gaining interests for highperformance applications

Denmark 3d Ic 2 5d Ic Packaging Market

High End Performance Packaging 3d 2 5d Integration I Micronews

Yole's advanced packaging team proposes a packaging technology segmentation and highlights with this new analysis, the impact of Internet of Things and the adoption of 25D/3D, FanOut and FanIn solutions "A transformation of the semiconductor industry is under way," announces Andrej Ivankovic, YoleWe cover modeling, lighting, materials, and moreSamsung Foundry Certifies Cadence System Analysis and Advanced Packaging Design Tool Flow for 25/3D Chip Designs Proven flow featuring the Celsius Thermal Solver and Clarity 3D Solver accelerates 25/3D designs for hyperscale, communications and

Toward 2 5 3d Packaging Enablement Through Copper Pillar

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

Packaging Materials for 25/3D Technology Brian Schmaltz Brian Schmaltz NAMICS Technologies, 55 Gateway Place San Jose, CA schmaltz@namicsusacom Search for other works by this author on This Site PubMed Google ScholarUse the model to for your product Include supplier specific details and incoming die preparation in your analysis View the detailed costs—including labor, material, capital, tooling, and yield impacts—for every step Labor rate Lot size Overhead rateTitleMaterials, Formulation, and Processes for Semiconductor, 25 and 3D Chip Packaging, and High Density Interconnection PCB DescProceedings of a meeting held 30 September 4 October 18, Cancun, MexicoAiMES 18 SeriesECS Transactions Volume 86 No08 EditorDow, WP et al ISBN Pages49 (1 Vol) FormatSoftcover TOCView Table of Contents

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2 5d And 3d Designs Semiwiki

Includes COVID19 impact on all forecastsSee how Studio helps you design packaging in 3D Work on oneup files, on multipart packaging and on POP displaysTry it for free httpsSelect a packaging style, quantity, and choose from custom or stock sizes – then start designing your custom boxes Add customization options like images, text, and any color your brand requires As you design you'll see an instant quote so you know exactly what your final order will come to Get started now Tiny minimums

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

Advanced Packaging Market Growing 6 6 Cagr To Reach 42bn In 25

25/3D Packaging Path Finding 25D/3D packaging technologies are revitalizing creativity in high technology products We thought we knew what faster, better, lighter and smaller meant 25D/3D packaging can revolutionize what we thought possible but it will require augmenting our current methods and tools One key methodology to add would beADVANCED PACKAGING PLATFORMS Focus on 3D stacking packaging platforms in this report No substrate FanOut WLCSP Organic substrates Wirebond BGA CSP COB BOC WB CSP LGA FlipChip BGA FC BGA FO on Substrate 25/21D 3D* CSP LGA Leadframe substrates Wire Bond QFN/QFP SOIC TSOP LCC DIP Flip Chip FC QFN (MIS) Ceramic substrates Wirebond Hi Rel FlipAdopters of silicon and glass based interposer fabrication The material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV Introduction

2 5 3d Packaging Path Finding 3d Incites

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

2D graphical projections and similar techniquesMarket updates 19 Sample wwwyolefr ©19 In this report ADVANCED PACKAGING PLATFORMS Focus on 3D stacking packaging platforms in this report No substrate FanOut WLCSP Organic substrates Wirebond BGA CSP COB BOC WB CSP LGA FlipChip BGA FC BGA FO on Substrate 25/21D 3D*Wafer Level Integration Technology &

Eps Ieee Org

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

25D and 3D packaging can provide significant size and performance advantages over other packaging technologies However, these advantages usually come at a high price Since 25D and 3D packaging costs are significant, today they are only used if no other option can meet the product requirements, and most of these applications are relatively low volume

Intel Leans Hard On Advanced Chip Packaging Technologies In Battle For Computing Supremacy Venturebeat

2 5d Semiconductor Engineering

3d Packaging Breaking New Ground Yole Pradeep S Techpoints

17 European 3d Summit Making Advanced Packaging Great Again

Advanced Semiconductor Packaging Starting To Change Memory Market Landscape Seeking Alpha

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

2 5d 3d Ic Market Challenges Opportunities

Three Dimensional Integrated Circuit Wikipedia

Figure 3 1 From Microelectronics Packaging Technology Roadmaps Assembly Reliability And Prognostics Semantic Scholar

Different 3d Technologies Arranged According To Manufacturing Costs And Download Scientific Diagram

High End Performance Packaging 3d 2 5d Integration I Micronews

O0f06lmxhslp1m

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

Semiconductor Packaging 2 5d 3d And Beyond High Technology Business Development Ira Feldman

Advanced Packaging Osats Foundries And Idms Part Of The Game

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Russia 3d Ic And 2 5d Ic Packaging Market Prospects Trends Analysis Market Size And Forecasts Up To 24

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

Nepp Nasa Gov

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

2 5d 3d Packaging Applications Indium Corporation

1

Ewh Ieee Org

Cetimes Com

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

Webinar Design Methodologies For Next Generation Heterogeneously Integrated 2 5 3d Ic Designs Semiwiki

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

3d Ic And 2 5d Ic Packaging Market Size Share Trends Analysis Industry Report 24 Igr

Pin On Telecharger Gratuit

Eetimes 3d Ic Design

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

Advanced Packaging Five Trends To Watch In 17 Electronic Products

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

3d Ic And 2 5d Ic Packaging Market Global Industry Analysis Trends Market Size And Forecasts Up To 24

Yole Developpement 3d Packaging Free Webcast On May 27 Yole Dev System Plus Consulting Join Forces To Share Their Expertise On The 2 5d 3d Packaging We Will Also

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

3d Ic And 2 5d Ic Packaging Global Market Trajectory Analytics

2 5d 3d Ase Group

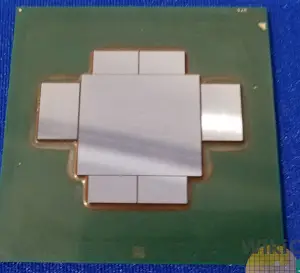

Amd Discloses Its Multi Layer Chiplet Design Era Starting With Zen 3 With 3d Stacked V Cache Technology

Flexible Multi Sensor Metrology Tool For Advanced Packaging Quote Rfq Price And Buy

2 5d 3d Ase Group

High End Performance Packaging 3d 2 5d Integration I Micronews

About 2 5d Technology Nhanced Semiconductors Inc

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

What Is 3d Integration 3d Incites

Fan Out Wafer Level Packaging The Samtec Blog

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

2 5d 3d Ase Group

2 5d Vs

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

2 5d 3d Packaging Applications Indium Corporation

Introducing Tsmc 3dfabric Tsmc S Family Of 3d Silicon Stacking Advanced Packaging Technologies And Services Taiwan Semiconductor Manufacturing Company Limited

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Now You Can Automate Latch Up Verification For 2 5 3d Technologies

High Performance Packaging Industry Focus And Intel Foveros

Advanced Packaging S Next Wave

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

Nist Gov

Sorting Out Packaging Options

3d Thursday 28nm Design And 2 5d Packaging Saves Xilinx A Ton Of Power You Can Too Even If You Re Not Designing Fpgas Eda360 Insider

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

Buy 3d Ic And 2 5d Ic Market By Packaging Technology 3d Tsv 3d Wafer Level Chip Scale Packaging 2 5d Application Imaging Optoelectronics Logic Mems Sensors Memory Led Power Region And End User Industry

More 2 5d 3d Fan Out Packages Ahead

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

The Race To Next Gen 2 5d 3d Packages

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

Global 3d Ic And 2 5d Ic Packaging Market 17 Taiwan

Left Right Above And Under Intel 3d Packaging Tech Gains Omnidirectionality Wikichip Fuse

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design